# Faculty of Engineering & Technology Third Semester B.E. (Computer Technology) (C.B.S.) Examination

## COMPUTER ARCHITECTURE AND ORGANIZATION

#### Paper-V

## Time—Three Hours] [Maximum Marks—80 INSTRUCTIONS TO CANDIDATES

- (1) All questions carry marks as indicated.

- (2) Due credit will be given to neatness and adequate dimensions.

- (3) Assume suitable data wherever necessary.

- (4) Diagrams should be given wherever necessary.

- (5) Illustrate your answers wherever necessary with the help of neat sketches.

- (a) Write an Assembly Language Program using loop that multiplies two positive numbers by using repeated addition. For example, to multiply 3 and 6, the program would add 3 six times, or 3+3+3+3+3.

- (b) Write an Assembly Language Program to add five numbers stored in the memory.

### www.solveout.in

- (c) Consider the following possibilities for saving the return address of a subroutine:

- (i) In a processor register

- (ii) In a memory location associated with the call, so that different location is used when subroutine is called from different places.

- (iii) On a stack.

Which of these possibilities supports subroutine nesting and which supports subroutine recursion and why?

#### OR

- 2. (a) Register R<sub>2</sub> is used in a program to point to the top of stack containing 32-bit numbers. Write a sequence of instruction using Index, Autoincrement and Autodecrement addressing modes to perform each of following tasks:

- Pop two items off the stack, add them and push result onto stack.

- (ii) Copy fifth element from top into register R2.

- (iii) Remove top ten items from the stack.

For each case, assume stack contains ten or more elements.

MIS-49274

2

Contd.

7

- (b) What do you mean by addressing mode? Explain 2 with example the necessity of different addressing modes?

8

- Write control sequence for execution of following instruction

SUB (R,) +, 1000

clearly mention each step by giving its function performed. Assume single bus processor architecture and each instruction consists of two words. 6

(b) Explain instruction formats used in IBM 370.

#### OR

- 4. (a) Explain 3 bus architecture with neat diagram. 6

- (b) Write a program to evaluate the expression

$$(A \times B + C \times D)/E * F$$

- In a single accumulator processor, assume that processor has Load, Store, Multiply and add instruction and that all values fit in accumulator.

- (ii) Write a program using stack.

- (iii) Write a program assuming three address instruction. 2.5+2.5+2

MIS-49274

Contd.

### www.solveout.in

(a) Give microinstruction for

Add R<sub>src</sub> (R<sub>dst</sub>)

(b) Explain the difference between hardwired control and microprogrammed control with neat diagram. Is it possible to have a hardwired control associated with a control memory?

#### OF

- 6. (a) In a computer instruction format, the instruction length is 11 bits and size of an address field is 4 bits. Is it possible to have:

- 5, 2-address instructions

- 45, 1-address instructions

- 32, 0-address instructions

using this format? Justify your answer.

- (b) Explain horizontal and vertical organization used in microprogrammed control.

- (a) What are guard bits? How can guard bits be removed? State their necessity.

(b) Describe the implementation of 4 bit carry look ahead adder. How can it be extended to higher number of bytes? What is maximum gate delay generated by a 4 bit parallel binary adder and how can it be minimized by carry look ahead adder?

ΛD

(a) Divide 38 by 7 using non-restoring division method. 5

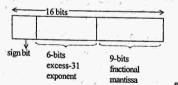

(b) Consider the floating numbers are represented in 16-bit format, as shown in figure. Represent 12.5 and – 6.25 in this format. Also multiply these two numbers using floating point multiplication algorithm.

9. (a) Design 4 M × 32 memory using 512 k × 8 static memory chips.

MIS-49274 4

Contd

5

MIS-49274

Contd

## www.solveout.in

|     |       | 705.21                                                                                                       |            |                  |                                                   |                      |                                         |

|-----|-------|--------------------------------------------------------------------------------------------------------------|------------|------------------|---------------------------------------------------|----------------------|-----------------------------------------|

|     | (b)   | What is virtual memory? With suitable diagram explain whow logical address is converted to physical address. |            | (a               | Vrite short notes  a) Vector proces  Array proces |                      | :                                       |

|     |       | OR                                                                                                           | 4          | (c               |                                                   |                      |                                         |

| 10. | (a)   | With neat sketch, explain the utility of memory                                                              |            |                  | , Cole M                                          |                      |                                         |

|     |       | interleaving.                                                                                                | 1 11 1     | (d               | <ol> <li>Flynn's classi</li> </ol>                | fication of parallel | structure. 14                           |

|     | (ь)   | time and dressable main                                                                                      | 1          | 4                |                                                   | 1                    | .,                                      |

|     |       | memory of 2 <sup>16</sup> bytes and block size of 8 bytes.                                                   | *          |                  |                                                   | 1                    |                                         |

|     |       | Assume direct mapped Cache consists of 32 cache                                                              | . 1        |                  |                                                   |                      | •                                       |

|     |       |                                                                                                              | į          |                  | *                                                 | 4                    |                                         |

| *1  |       | blocks:                                                                                                      |            |                  |                                                   | 1.1                  |                                         |

|     |       | (i) How is 16-bit main memory address divided?                                                               | 12.0       |                  | \$ 5                                              |                      | - x - x - x - x - x - x - x - x - x - x |

|     |       | (ii) Into what block would bytes with each of the                                                            | - /4 - /   |                  |                                                   | er at in             |                                         |

| -   |       | following addresses be stored?                                                                               | was proces | للبيدة والأسارات |                                                   | 1-4-4, :             | ووالمرامة                               |

| ,   |       | 0001 0001 0001 1011                                                                                          | 1          |                  |                                                   | 1                    |                                         |

|     |       | 1100 0011 0011 0100.                                                                                         |            |                  |                                                   |                      |                                         |

|     | 1     | (iii) How many total bytes of memory can be stored                                                           | - 1        | 1                |                                                   |                      |                                         |

| *.  |       | in Cache?                                                                                                    |            |                  |                                                   |                      |                                         |

|     |       |                                                                                                              |            |                  |                                                   |                      |                                         |

|     |       | (IV) Wily tag is stored in cut-                                                                              |            |                  |                                                   |                      | •                                       |

| 11. | (a)   | Give features of RISC processor. 5                                                                           | 7"         |                  |                                                   | 2.5                  |                                         |

|     | (b)   | What is interrupt service routine? Explain different                                                         | *          | y .              |                                                   | 7.5                  |                                         |

|     | (0)   | mechanism available for handling interrupts. 9                                                               | -          |                  |                                                   |                      |                                         |

|     |       | OR                                                                                                           |            |                  |                                                   | * * 4.3              |                                         |

|     |       | Contd                                                                                                        | 1          |                  |                                                   | 1                    |                                         |

| M   | IS-49 | 274 6 Contd.                                                                                                 |            | MIS-492          | 74                                                | 7                    | 1000                                    |