KNT/KW/16/7325/7330

P.T.O

Design an op amp circuit to implement the following specification or expression

$V_0 = 3V_1 - 2V_2 + 2V_3 + 2V_4$

Assume  $R_F = 100 \text{ K} \Omega$

a)

b) Draw the circuit of instrumentation amplifier using three op amp and derive the expression 7 for output voltage V<sub>0</sub>.

## OR

6

6

6

14

**4.** a) Design integrator circuit to implement following equations:

$$V_0 = \frac{-1}{3} \int V_1 dt \frac{-1}{2} \int V_2 dt - \int V_3 dt$$

Where  $V_1$ ,  $V_2$  and  $V_3$  are input voltages &  $V_0$  is the O/P voltages

- b) Draw the circuit of practical temperature compensated logarithmic amplifier and derive an **8** expression for output voltage.

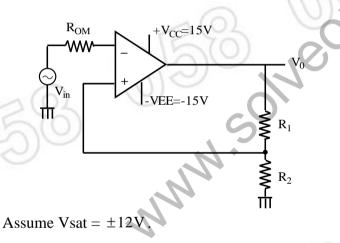

- 5. a) For a Schmitt trigger circuit using op amp. Shown in fig (5) a. find out the value of VLT & 7 Vut & VH. Assume  $R_1 = 82 \text{ K} \Omega$ ;  $R_2 = 2\text{ K} \Omega$ .

- b) Draw & explain precision full wave rectifier.

- 6. a) Design as table multivibrator using IC 555 to generate square wave output with 50% duty 7 cycle at 5 KHz. Assuming capacitor =  $0.01 \,\mu\text{F}$

OR

b) Draw and explain R - 2R ladder type D to A Converter.

Design SVR to give 5 V output at maximum load current of 200mA. Assume that unregulated input is 12 V $\pm$ 10% V with source resistance 1  $\Omega$ . Determine Sv & Ro. Assume transistor having  $h_{fe_1} = 60$  and  $h_{fe_2} = 100$ .

OR

KNT/KW/16/7325/7330

Design a stepdown SMPS to give 5V.  $I_0 = I_L = 8$  Amp. unregulated input is 20 V, switching frequency is 25 KHz. Assume reference voltage is 2V. Vsat = 1.2 V. tsw = 1.1 µsec. &  $V_{DON} = 1V$ . The output ripple should be limited to less than 80mV(P-P). Also calculate the efficiency of SMPS.

14

7

6

8

5

7

6

- 9. a) Design Rc phase shift oscillator for the following specifications:  $V_0 \ 8 \ V$  peak to peak, frequency of oscillations = 10 KHz, Also determine frequency shift if phase shift of 1° is introduced in the loop.

- b) Derive the frequency of oscillation for wein bridge oscillator.

## OR

- **10.** a) Derive an expression for figure of merit for Hartley oscillator.

- b) Write a technical short notes on design of diode function generator.

- a) Design Butterworth filter such that relative attenuation is less than 1dB for frequencies below 500 Hz and greater than 17 dB for frequencies above 1 KHz.

- b) Design 4<sup>th</sup> order high pass filter with cut off frequency of 8 KHz. (Assume  $C = 0.1 \mu F$ )

## OR

- a) Design a bandpass filter using IGMF techniques to give a band pass gain 5 centre frequency 7

8 KHz and bandwidth 1 KHz. Calculate the value of R<sub>2</sub>.

- b) Write short note on **any one.**

11.

- i) Design of Relay driver circuit.

- ii) Design of First order LPF.

\*\*\*\*\*

KNT/KW/16/7325/7330