# NTK/KW/15/7545

Faculty of Engineering & Technology

Seventh Semester B.E. (EC/ET) (C.B.S.) Examination

ELECTIVE—I: VLSI SIGNAL PROCESSING

Time—Three Hours] [Maximum Marks—80

## INSTRUCTIONS TO CANDIDATES

- (1) All questions carry marks as indicated.

- (2) Solve Question No. 1 OR Question No. 2.

- (3) Solve Question No. 3 OR Question No. 4.

- (4) Solve Question No. **5 OR** Question No. **6**.

- (5) Solve Question No. 7 OR Question No. 8.

- (6) Solve Question No. 9 OR Question No. 10.

- (7) Solve Question No. 11 OR Question No. 12.

- (8) Due credit will be given to neatness and adequate dimensions.

- (9) Assume suitable data wherever necessary.

- (10) Illustrate your answers wherever necessary with the help of neat sketches.

- (11) Use of non programmable calculator is permitted.

9. Construct a  $2 \times 3$  convolution algorithm using winograd algorithm with  $M(P) = P(P-1) (P^2 + 1)$ .

## OR

10. (a) Explain the steps in modified Cook Toom algorithm.

5

- (b) Constract a 2  $\times$  2 convolution algorithm using Cook-Toom algorithm with b = 0,  $\pm$  1.

- 11. (a) Explain steps of iterated convolution algorithm. 3

- (b) Construct a 4×4 linear convolution algorithm using 2 × 2 short convolution. 10

#### OR

12. Construct a  $4 \times 4$  cyclic convolution algorithm using CRT with

$$m(P) = P^4 - 1 = (P - 1) (P + 1) (P^2 + 1)$$

. 13

- 1. (a) Explain the structure of direct form FIR filter & data broadcast form FIR filter. Show that the data broadcast form can achieve a faster clock rate.

- (b) It is necessary to reduce the power consumption of a system by at least 5 times using pipelining. For the threshold voltage of 0.4 V and initial supply voltage of 5V, at what level should the system be pipelined? What is the supply voltage of the pipelined system?

#### OR

- 2. (a) How pipelining can be used to reduce power consumption? Explain in detail.

- (b) Show that parallel processing reduces the power consumption of a system.

- 3. (a) What is retiming? Explain the method of retiming which uses cutest in combination of slowdown. 6

- (b) Explain properties of retiming with example.

## OR

4. Draw a constraint graph and use it to determine if the following system of inequalities has a solution and find a solution if one exists using Bellman-Ford algorithm. 13

$$\begin{split} & r_1 - r_2 \leq 0 \\ & r_3 - r_1 \leq 5 \\ & r_4 - r_1 \leq 4 \\ & r_4 - r_3 \leq -1 \\ & r_3 - r_2 \leq 2 \end{split}$$

- 5. (a) Show that unfolding preserves the total no. of delays.

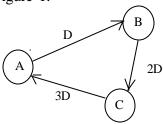

- (b) Perform Unfolding with unfolding factor J=3 for the given Figure 1.

OR

- 6. Describe how to design parallel processing architectures using unfolding.

- 7. (a) Explain the folding algorithm.

- (b) Explain life-time analysis for register minimisation.

7

#### OR

8. Consider a DSP program that performs transpose operation of  $3 \times 3$  matrix shown below.

Find:

- (1) Life time analysis

- (2) Data allocation using forward backward

- (3) Register minimization.

13

The matrix is:

$$\begin{bmatrix} a & b & c \\ d & e & f \\ g & h & i \end{bmatrix}$$

MVM—47639 2 Contd.

MVM—47639 3 Contd.